| Seat No.: Enro | llment No. |

|----------------|------------|

|----------------|------------|

## **GUJARAT TECHNOLOGICAL UNIVERSITY**

BE – SEMESTER-III (NEW) • EXAMINATION – SUMMER-2015

| Subject Code: 2132003 Subject Name: Design Concepts in Basic Electronics Time:02.30pm-05.00pm Instructions: |            | Date:27/05/2015  Total Marks: 70                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |            |

|-------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|

|                                                                                                             |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |            |

| Q.1                                                                                                         | (a)<br>(b) | <ol> <li>Answer the following question.         <ol> <li>Define Digital System.</li> <li>Convert (2C6B.F2)<sub>16</sub> into its equivalent Binary.</li> <li>Convert (8)<sub>10</sub> into equivalent BCD and Excess-3 code.</li> <li>Convert (414)<sub>8</sub> into its equivalent Hexadecimal and Binar</li> </ol> </li> <li>Comparison between 1's and 2's compliments.</li> <li>Explain Digital Logic Gates with Symbol, Algebraic function an</li> </ol> |                   | 03         |

| Q.2                                                                                                         | (a)        | 1) State the truth table of full-adder and half-adder.                                                                                                                                                                                                                                                                                                                                                                                                        |                   | 0.         |

|                                                                                                             | <b>(b)</b> | 2) Draw the logic diagram and state truth table of 4x1 multiplex Draw and Explain the working of clocked RS flip-flop.  OR                                                                                                                                                                                                                                                                                                                                    | er.               | 04         |

|                                                                                                             | <b>(b)</b> | Draw and Explain the working of JK flip-flop.                                                                                                                                                                                                                                                                                                                                                                                                                 |                   | 0'         |

| Q.3                                                                                                         | (a)<br>(b) | Design 4-bit up-down binary counter with the help of T flip-flop<br>Define term Register. Define the 'Different Modes of Operation<br><b>OR</b>                                                                                                                                                                                                                                                                                                               |                   | 0′<br>0′   |

| Q.3                                                                                                         | (a)<br>(b) | With the logic diagram explain the operation of 4-bit binary ripp Explain with neat diagram working of 4-bit bidirectional shaparallel load.                                                                                                                                                                                                                                                                                                                  |                   | 0'.<br>0'. |

| Q.4                                                                                                         | (a)<br>(b) | Explain Forward Bias and Reverse Bias.  Give the points of difference between Half wave, Full wave and OR                                                                                                                                                                                                                                                                                                                                                     | Bridge Rectifier. | 0'.<br>0'. |

| Q.4                                                                                                         | (a)<br>(b) | Explain in detail different types of breakdown in diode.<br>Explain different configuration of clippers.                                                                                                                                                                                                                                                                                                                                                      |                   | 0'.<br>0'. |

| Q.5                                                                                                         | (a)        | Explain the input output characteristics of n-p-n transistor in Coconfiguration.                                                                                                                                                                                                                                                                                                                                                                              | ommon-Collector   | 0'         |

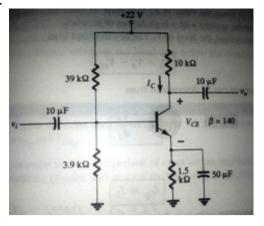

|                                                                                                             | <b>(b)</b> | Draw fixed-bias circuit and explain Collector-Emitter loop.  OR                                                                                                                                                                                                                                                                                                                                                                                               |                   | 0'         |

| Q.5                                                                                                         | (a)        | Explain the input output characteristics of p-n-p transistor in configuration.                                                                                                                                                                                                                                                                                                                                                                                | Common-Emitter    | 0′         |

**07**

\*\*\*\*\*