## **GUJARAT TECHNOLOGICAL UNIVERSITY** BE – SEMESTER – VI (NEW).EXAMINATION – WINTER 2016

## Subject Code: 2161004 Date: 26/10/2016 Subject Name: VLSI Design Time: 02:30 PM to 05:00 PM **Total Marks: 70 Instructions:** 1. Attempt all questions. 2. Make suitable assumptions wherever necessary. 3. Figures to the right indicate full marks. **Q.1** (a) Explain the importance of Regular, Modular and Local Architecture for VLSI. 07 Also give one example for each. (b) Explain the fabrication steps of NMOS transistor with necessary figures 07 Q.2 What do you understand by gradual channel approximation? Derive expression 07 **(a)** for the drain current flowing through n-channel MOSFET as a function of V<sub>GS</sub>, $V_{DS}$ , and $V_{BS}$ . (b) Calculate the threshold voltage $V_{TO}$ at $V_{SB}= 0$ , for a polysilicon gate n-channel 07 MOS transistor, with the following parameters: Substrate doping density $N_A = 10^{16} \text{ cm}^{-3}$ , Polysilicon gate density $N_D=2 \times 10^{20} \text{ cm}^{-3}$ , Gate oxide thickness tox=500 Angstrom and Oxide interface fixed charge density $N_{ox} = 4 \times 10^{10} \text{ cm}^{-2}$ , $\phi_{\rm F}({\rm gate}) = 0.55 {\rm V}.$ **Physical constants :** Thermal voltage =KT/q = 0.026 volt. Energy Gap of silicon (Si) = $E_g = 1.12$ Ev. Intrinsic Carrier Concentration of silicon= $n_i=1.45 \times 10^{10} \text{ cm}^{-3}$ . Dielectric constant of vaccume = $\varepsilon_0$ =8.85 x 10-<sup>14</sup>F/cm. Dielectric constant of silicon = $\varepsilon_{si}$ = 11.7 x $\varepsilon_{o}$ F/cm. Dielectric constant of silicon dioxide = $\varepsilon_{ox}$ = 3.97 x $\varepsilon_{o}$ F/cm OR (b) For an enhancement type NMOS transistor $V_{T0}= 0.8 \text{ V}$ , $\lambda = 0.05 \text{ 1/V}$ , process 07 transconduction $\mu_n * C_{ox} = 20 \text{A/V}^2$ , W/L = 20 $\mu$ m, $\gamma = 0.2 \text{ V}^{1/2}$ , 2 $\varnothing$ F=0.58 VV<sub>G</sub>= 5V, V<sub>D</sub>=4V, V<sub>S</sub>=2V, Calculate Drain Current I<sub>D</sub> 07 (a) Draw the inverter circuit with depletion type NMOS load. Mention the

- Q.3 (a) Draw the inverter circuit with depletion type NMOS load. Mention the 07 operating regions of driver and load transistors for different input voltages. Derive critical voltage points V<sub>OH</sub>, V<sub>OL</sub> and V<sub>IL</sub> and V<sub>IH</sub> for depletion- load NMOS inverter

- (b) Explain Elmore delay model for CMOS inverter with appropriate diagram and explain how rise time and fall time are computed if inverter is driving another inverter

## OR

- **Q.3** (a) Define  $\tau_{PHL}$  and  $\tau_{PLH}$  for CMOS inverter. Draw input and output waveforms 07 during high to low transition of output for a CMOS inverter Derive  $\tau_{PHL}$  for CMOS inverter

- (b) Design a resistive load inverter with  $R = 1k\Omega$ , such that VOL = 0.6V. The **07** enhancement-type nMOS driver transistor has the following parameters:  $V_{DD} = 5.0V, V_{TO} = 1.0 V, \gamma = 0.2 V^{1/2}, \lambda = 0, \mu_n * Cox = 22.0 \mu A/V^2$ a. Determine the required aspect ratio, W/L. b. Determine  $V_{IL}$  and  $V_{IH}$ .

- Q.4 (a) What is Euler path approach? Draw the optimized stick-diagram for the following Boolean function (CMOS Logic ), X = A(D + E) + BC. Explain the importance of Euler path approach.

- (b) Draw negative edge triggered Master slave D flip flop and explain its working 07

OR

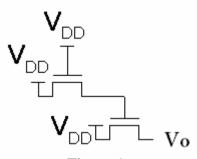

Q.4 (a) Explain the basic principle of pass transistor, using Logic "1" transfer event and logic "0" event. For the NMOS pass transistor circuit shown in figure 1 below, find Vo.

Figure 1

- (b) Write a short note on CMOS Transmission Gate. Explain its usefulness. Draw 2:1 MUX using compound gate and compare it with 4:1 MUX based on transmission gate. Also draw 8:1 MUX based on transmission gate

- Q.5 (a) What is the need for voltage bootstrapping? Explain dynamic voltage bootstrapping 07 circuit with necessary mathematical analysis.

- (b) List Ad-hoc testable design techniques and discuss any two in detail 07

## OR

- Q.5 (a) Write a short note on Built In Self Test (BIST). 07

- (b) Why do we need isolation between MOS transistors fabricated on a single chip? 07

Explain etched field-oxide isolation and LOCOS isolation techniques with diagrams

\*\*\*\*\*