## **GUJARAT TECHNOLOGICAL UNIVERSITY** BE - SEMESTER-III • EXAMINATION – WINTER • 2014

| Subject Code: 2132003 Date: 20-12-2 |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Tiı                                 | me: 0<br>tructio<br>1.                                                                                                          | Attempt all questions.<br>Make suitable assumptions wherever necessary.                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| Q.1                                 | <ul> <li>(a)</li> <li>(1)</li> <li>(2)</li> <li>(3)</li> <li>(4)</li> <li>(5)</li> <li>(6)</li> <li>(7)</li> <li>(b)</li> </ul> | Answer the following question.<br>Define Digital Signal.<br>Convert $(145)_{10}$ into its equivalent Binary.<br>Convert $(100101010110)_2$ into its equivalent Octal and Hexadecimal number.<br>Convert $(1F67.546)_{16}$ into its equivalent Decimal.<br>Convert $(6)_{10}$ in to equivalent BCD, Gray code and Excess-3 code.<br>State the truth table of Full-Adder.<br>State excitation table and characteristics table for J K Flip Flop.<br>Prove the following using Truth Table. | 07       |

|                                     | (1)<br>(2)                                                                                                                      | $\overline{A} + \overline{B} + \overline{C} = \overline{(A \cdot B \cdot C)}$ $XY + \overline{X}Z + YZ = XY + \overline{X}Z$                                                                                                                                                                                                                                                                                                                                                             | 07       |

| Q.2                                 | (a)<br>(b)                                                                                                                      | Explain in detail different type of breakdown in diode.<br>Simplify the following Boolean function using Karnaugh map method and realize with minimum NAND gates only.<br>Function F (A,B,C,D) = $\sum (0,1,2,8,9)$ and don't care conditions: d(A,B,C,D) = $\sum (3, 5,10,13)$                                                                                                                                                                                                          | 07<br>07 |

|                                     | (b)                                                                                                                             | OR<br>Reduce following Boolean expression in minimum number of literals. (ANY<br>TWO)                                                                                                                                                                                                                                                                                                                                                                                                    | 07       |

|                                     | (1)                                                                                                                             | AB + A(B + C) + B(B + C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

(1) AB + A(B + C) + B(B + C)

(2)  $\overline{X}YZ + XZ + \overline{X}Z$

- Q.3 (a) Design 3 bit up down synchronous counter with help of T flip flop. 07

- (b) Give the points of difference between half wave, Full wave, and Bridge 07 rectifier.

- **Q.3** (a) Show that NAND and NOR are universal gate.

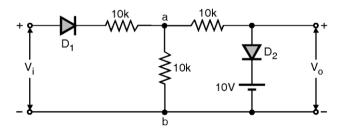

- (b) The diodes are ideal, plot Vo against Vi indicating all intercepts, slopes and 07 voltage levels for Fig. and Sketch Vo if Vi = 40 sin  $\omega t$ .

- Q.4 (a) Explain with neat diagram working of 8x1 multiplexer and 3to8 decoder. 07

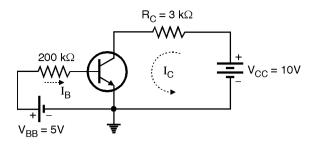

- (b) For the transistor shown in Fig,  $\beta = 100$ . Find the transistor currents and state in **07** which region it is operating. Assume that it is a silicon transistor

07

## OR

- Q.4 (a) Explain with neat diagram working of 4-bit bidirectional shift register with 07 parallel load

- (b) Explain in details effect of temperature, transistor and collector current on  $\beta_{dc}$  07

- Q.5 (a) Explain the input output characteristic of n-p-n transistor in CE configuration. 07 Also indicate different regions.

- (b) Explain with neat diagram Voltage divider bias

- OR

- Q.5 (a) Explain the input output characteristic of n-p-n transistor in CB configuration. 07 Also indicate different regions.

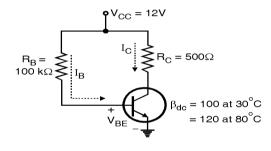

- (b) The fixed bias circuit of Fig. a silicon transistor is uses. The component values 07 are  $R_C = 500 \ \Omega$  and  $R_B = 100 \ k\Omega$ .  $\beta_{dc}$  of the transistor is 100 at 30°C. Determine Q point co-ordinates at 30°C.

\*\*\*\*\*

07