| Seat No.:   |                                                                                              | Enrolment No                                                                                                                                   |                  |  |  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|--|--|--|

|             |                                                                                              | GUJARAT TECHNOLOGICAL UNIVERSITY                                                                                                               |                  |  |  |  |  |  |  |

|             |                                                                                              | M. E SEMESTER – II • EXAMINATION – SUMMER • 2017                                                                                               |                  |  |  |  |  |  |  |

| Subject     | code:                                                                                        | 2724204 Date: 30-05-2                                                                                                                          | Date: 30-05-2017 |  |  |  |  |  |  |

| Subject 1   | Name                                                                                         | e: HDL BASED DESIGN WITH PROGRAMMABLE LOGIC                                                                                                    |                  |  |  |  |  |  |  |

| Time: 02    | 2:30 p                                                                                       | om - 05:00 pm Total Marks                                                                                                                      | s: 70            |  |  |  |  |  |  |

| Instruction | ons:                                                                                         |                                                                                                                                                |                  |  |  |  |  |  |  |

| 2.          | Make                                                                                         | mpt all questions.<br>e suitable assumptions wherever necessary.<br>res to the right indicate full marks.                                      |                  |  |  |  |  |  |  |

| Q.1 (a)     | Do a                                                                                         | as Directed.                                                                                                                                   | 14               |  |  |  |  |  |  |

|             | 1.                                                                                           | VHDL is a strongly typed language. (True/False)                                                                                                |                  |  |  |  |  |  |  |

|             | 2.                                                                                           | Name any one system (Hw/Sw) description language. (SystemC)                                                                                    |                  |  |  |  |  |  |  |

|             | Sensitivity list in the process statement is a type of Implicit Wait statement. (True/False) |                                                                                                                                                |                  |  |  |  |  |  |  |

|             | 4.                                                                                           | Which VHDL construct is used for developing parameterized designs?                                                                             |                  |  |  |  |  |  |  |

|             | 5.                                                                                           | The 'next' statements skip the remaining statement in the iteration of                                                                         |                  |  |  |  |  |  |  |

|             |                                                                                              | loop and execution starts from first statement of next iteration of loop.                                                                      |                  |  |  |  |  |  |  |

|             |                                                                                              | <b>a.</b> Previous <b>b.</b> Next <b>c.</b> Current (present) <b>d.</b> None of the above                                                      |                  |  |  |  |  |  |  |

|             | 6.                                                                                           | Which among the following wait statement execution causes the enclosing process to suspend and then wait for an event to occur on the signals? |                  |  |  |  |  |  |  |

|             |                                                                                              | <b>a.</b> Wait until Clk = '1' <b>b.</b> Wait on x,y,z                                                                                         |                  |  |  |  |  |  |  |

|             | -                                                                                            | <b>c.</b> Wait on clock until answer > 80 <b>d.</b> Wait for 12 ns                                                                             |                  |  |  |  |  |  |  |

|             | 7.                                                                                           | In Net-list language, the net-list is generatedsynthesizing VHDL code.  (Before/After)                                                         |                  |  |  |  |  |  |  |

|             | 8.                                                                                           | What is the usage of ALLIAS in VHDL?                                                                                                           |                  |  |  |  |  |  |  |

What do you mean by resolution function in VHDL?

Mention the popular design approaches used in VLSI design.

which more flexibility is required - CPLD or FPGA? Why?

1. Discuss various types of delay models supported in VHDL? (3 Marks)

2. What do you mean by VLSI Design Quality? Discuss any four. (4 Marks)

Explain what are the various levels of abstractions in VLSI design?

Event driven simulator captures information on internal nodes also. – True/False

Which programmable hardware you will choose for implementing the design in

What are the components of a standard test-bench? Explain the usage of (others => ' ') statement in VHDL?

9. 10.

11.12.

14.

Q.2 (a)

(b)

07

07

## OR

- (b) What are the various modelling styles supported by HDLs? Discuss each one of them 07 with suitable example.

- Q.3 (a) Discuss pros and cons of Full Custom vs. Semi-custom VLSI design styles.

- (b) 1. Draw and explain the architecture of an FPGA. (4 Marks) 07

- 2. Current FPGAs are used as SoC Justify. (3 Marks)

## OR

- Q.3 (a) Write a VHDL description to implement 4-bit ALU with functions Addition, 07 Subtraction using 2's complement, Multiplication by 2, Division by 2.

- (b) Explain following design constructs in reference to VHDL.

- 1. ARRAYS 2. RECORDS

- Q.4 (a) What are the various logic implementation platforms available? Discuss in detail the selection criteria for the given application.

- (b) Discuss the differences between Event-Driven and Cycle-Based Simulation. Explain 07 the operation of Cycle based simulator in detail.

## OR

- Q.4 (a) Draw the Melay Machine state diagram for a sequence detector to detect an overlapping 07 sequence of "110". Write the VHDL code for the same.

- (b) What is synthesis? Explain following terms

- 1. RTL Synthesis

- 2. High Level Synthesis

- 3. Gate Level Synthesis

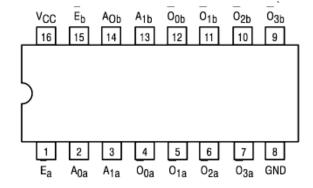

- Q.5 (a) The pin diagram and truth table for dual 2x4 line decode IC 74LS139 is shown below. 07 Write the VHDL description for implementing the functionality of the chip.

| TRUTH TABLE |                |                |         |    |    |    |  |  |  |  |

|-------------|----------------|----------------|---------|----|----|----|--|--|--|--|

|             | INPUTS         | 5              | OUTPUTS |    |    |    |  |  |  |  |

| Ē           | A <sub>0</sub> | A <sub>1</sub> | 00      | 01 | 02 | 03 |  |  |  |  |

| Н           | Χ              | Х              | Н       | Н  | Н  | Н  |  |  |  |  |

| L           | L              | L              | L       | Н  | Н  | Н  |  |  |  |  |

| L           | Н              | L              | Н       | L  | Н  | Н  |  |  |  |  |

| L           | L              | Н              | Н       | Н  | L  | Н  |  |  |  |  |

| L           | Н              | Н              | Н       | Н  | Н  | L  |  |  |  |  |

07

07

- (b) 1. Discuss the main differences between Verilog and VHDL. (4 Marks)

- 2. What do you mean by High Level Synthesis? (3 Marks)

OR

Q.5 (a) Prepare the PLA table to realize following Boolean functions. Draw the structure of the programmed PLA to produce normal output. Count the total number of programmable links required in the PLA.

$$F_1 = / (0,2,4)$$

$F_2 = % (0,1,3,7)$

$\frac{1}{F_3} = / (5,7)$

(b) Draw the RTL FOR below given VHDL code and rewrite the equivalent Verilog code for the same.

```

entity shift reg is

in std logic;

I: in std_logic; clock: in std_logic; shift: in std_logic; out std logic

out std logic

);

end shift reg;

______

architecture behv of shift reg is

-- initialize the declared signal

signal S: std logic vector(2 downto 0):="111";

begin

process(I, clock, shift, S)

begin

-- everything happens upon the clock changing

if clock'event and clock='1' then

if shift = '1' then

S \le I \& S(2 \text{ downto } 1);

end if;

end if;

end process;

-- concurrent assignment

Q \le S(0);

end behv;

```

**3of 3**

07