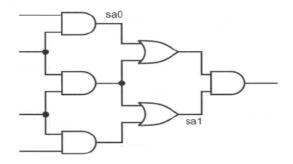

## **GUJARAT TECHNOLOGICAL UNIVERSITY** M. E. - SEMESTER - II • EXAMINATION - SUMMER • 2013 Date: 31-05-2013 **Subject code: 1724202** Subject Name: Testing and Verification of VLSI Design Time: 10.30 am – 01.00 pm **Total Marks: 70 Instructions:** 1. Attempt all questions. 2. Make suitable assumptions wherever necessary. 3. Figures to the right indicate full marks. (a) Write a test bench for 4 to 1 MUX. **Q.1** 07 (b) Justify significance of code coverage and functional coverage. 07 0.2 (a) Describe the need for scan chain and explain how it will be implemented? 07 (b) Write in Brief: 07 i) Design for verification ii)Verification Reuse. OR 07 (b) Write in Brief: i) Reconvergence model ii) Verification of reusable components. Q.3 (a) Explain various verification methodologies. Which verification methodology 07 you will choose after clock tree insertion? (**b**) Writ the difference between 07 i) Simulator and emulator ii) Third Party Model and Hardware modeler iii) Cycle based and event Driven Simulation OR **Q.3** (a) Explain In Brief: 07 i) Fault Equivalence ii) Controllability iii) Observabillity iv) Fault Masking v) Redundant fault vi) Pattern Sensitive Fault vii) On line testing (b) i) Why fault modeling at logical level is more preferred? 07 ii) Though test generation of multiple faults is possible why it is not attempted commonly? (a) Explain the stuck open fault for transistor with necessary example. 07 Q.4 (b) For a CMOS implementation of NAND gate find out the complete test vector 07 set for all the transistors are stuck open or stuck short. OR Q.4 (a) For a gate level implementation given below Find out 07 i) Total number of faults ii) Apply fault dominance and fault equivalence and find out fault collapsing ratio.

iii) list out the test set for faults shown in fig.

| <b>(b)</b> | For a gate level implementation of XOR gate only using NAND gate | 07 |  |

|------------|------------------------------------------------------------------|----|--|

|            | i) Calculate controllability at each net of the implementation   |    |  |

|            | ii) Find out Observability at each net.                          |    |  |

| Q.5 | ~ / | List out various adhoc DFT techniques and explain any two of them in brief.<br>Explain concept of random access scan. |  |

|-----|-----|-----------------------------------------------------------------------------------------------------------------------|--|

|     |     | OR                                                                                                                    |  |

| Q.5 | <b>(a)</b>  | What if roll of LFSR in Bist?     | 07 |

|-----|-------------|-----------------------------------|----|

|     | <b>(b</b> ) | What is the significance of ATPG? | 07 |

\*\*\*\*\*