|                            |            | Enrolment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|----------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 110                        |            | GUJARAT TECHNOLOGICAL UNIVERSITY<br>SEMESTER-EXAMINATION –                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| Subject code: 2722602 Date |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| Subj<br>Time               |            | Name: CMOS Circuit Design - II<br>Total Ma                                                                                                                                                                                                                                                                                                                                                                                                                                                         | l 70     |

| Instr                      | -          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | arks: /U |

| Insti                      | 1.<br>2.   | Attempt all questions.  Make suitable assumptions wherever necessary.  Figures to the right indicate full marks.                                                                                                                                                                                                                                                                                                                                                                                   |          |

| Q.1                        | (a)        | In SC non-inverting amplifier (see Fig. 1, Q:1 (a)), $S_1$ turns off t seconds after $S_2$ turns off, and $S_3$ turns on t seconds after $S_1$ turns off. Plot the output waveform taking into the charge injection and clock feedthrough of all switches. Assume all switches are implemented with NMOS. Provide supportive explanation for the plot drawn by you.                                                                                                                                | 07       |

|                            | (b)        | Draw and explain operation of multiply-by-two SC circuit. What should be sequence of operation of switches and why? Also draw its equivalent circuits for sampling and amplification phases.                                                                                                                                                                                                                                                                                                       | 07       |

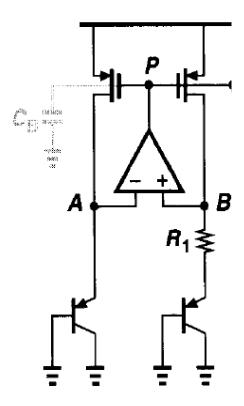

| Q.2                        | (a)        | Show that the output noise voltage is approximately same as input-referred noise voltage of op amp in the voltage reference generator circuit shown in Fig. 2, Q:2 (a). Neglect parasitic capacitance C <sub>B</sub> shown in the figure.                                                                                                                                                                                                                                                          | 07       |

|                            | (b)        | How does the op-amp input offset voltage affect the output voltage in temperature independent voltage reference circuit? What are the solutions to solve this problem? Draw the final circuit which has the less effect of op-amp input offset voltage and feasible for implementation in CMOS technology.                                                                                                                                                                                         | 07       |

|                            | <b>(L)</b> | OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 07       |

|                            | (b)        | <ul> <li>1. Suppose a type I (simple) PLL experiences a frequency step at t = 0. Calculate the change in phase error using Laplace transform.</li> <li>2. In type I PLL, an external voltage V<sub>ex</sub> is added to the output of low-pass filter. (a) Determine the phase error and V<sub>LPF</sub> if the loop is locked and V<sub>ex</sub> = V<sub>1</sub>. (b) Suppose V<sub>ex</sub> steps from V<sub>1</sub> to V<sub>2</sub> at t = t<sub>1</sub>. How the PLL will respond?</li> </ul> | • 7      |

| Q.3                        | (a)        | What do you understand by jitter? Show that the basic charge pump PLL behaves as low-pass filter for the jitter appearing in input signal and it behaves as high-pass filter for the jitter appearing in VCO signal.                                                                                                                                                                                                                                                                               | 07       |

|                            | <b>(b)</b> | Draw gross section of floating memory alament and avalain its                                                                                                                                                                                                                                                                                                                                                                                                                                      | 07       |

(b) Draw cross section of floating memory element and explain its 07

operation from the point of view of reading, writing and erasing.

OR

- (a) Explain with necessary diagrams and waveforms, the issue observed in basic 07 Q.3 charge pump PLL due to finite capacitance seen at the drains of current sources. Suggest possible solution to this problem.

- (b) In sensing flash memory using DSM, how can we dump a constant 07 charge independent of bit line voltage into bit line capacitor? Draw necessary circuit diagram and explain its operation.

- (a) Sketch a circuit for sensing resistive memory using a concept of DSM 07 **Q.4**

and derive expression of R<sub>mbit</sub>.

(b) Draw and explain the block diagram of voltage comparator. Discuss the operation of positive feedback decision circuit with necessary equations in detail.

## OR

- Q.4 (a) Illustrate operation of sense amplifier having rail-to-rail input range. 07 Discuss performance of the same from the point of view of kick-back noise, clock feed-through, power dissipation, and memory.

- (b) Describe operation CMOS analog multiplier along with circuit diagram 07 and mathematical analysis.

- Q.5 (a) Sketch general implementation of charge scaling DAC and explain its working 07 with necessary mathematical analysis.

- **(b)** Briefly discuss following parameters which play a critical role in the **07** overall performance and design of LNA.

- 1. Noise Figure

- 2. Input Return Loss

- 3. Stability

## OR

- Q.5 (a) Draw block diagram of dual slope ADC and explain its operation with 07 necessary mathematical analysis.

- **(b)** List out various LNA topologies. Explain quantitatively operation of **07** common source stage with inductive load LNA along with diagram.

\*\*\*\*\*

Fig. 1: Q:1 (a)

Fig. 2: Q:2 (a)