## **GUJARAT TECHNOLOGICAL UNIVERSITY** ME- SEMESTER II– EXAMINATION – SUMMER 2015

| Sub<br>Tim | ject ]<br>ie: 2:<br>uction<br>1.<br>2. | Code: 2724204       Date: 01/06/20         Name: HDL Based Design with Programmable Logic         30 PM – 5:00 PM       Total Marks: 7         is:         Attempt all questions.         Make suitable assumptions wherever necessary.         Figures to the right indicate full marks.                                                                                                                                                                                                                                                                 |    |

|------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Q.1        | (a)<br>(b)                             | <ol> <li>Write a VHDL statement to declare a port with following attributes         <ol> <li>Port name: DATABUS</li> <li>Width : 8bit (A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub>, í , A<sub>8</sub>)</li> </ol> </li> <li>Model a 3 i/p NAND gate with inertial delay of 5 ns? Draw the i/p ó o/p waveform.</li> <li>How many logic levels are supported by STD_ULOGIC data type? Which of them are synthesizable?</li> <li>Process statement can be used to describe sequential logic only. Justify whether the statement is True or False.</li> </ol> | 07 |

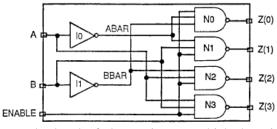

| Q.2        | <b>(a)</b>                             | Write the behavioral VHDL code to describe the given combinational circuit using PROCESS statement.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 07 |

- (b) 1. List and discuss the level of abstractions at which the Digital circuit can 07 be described. Comment on the accuracy vs. speed of simulation at each abstraction level. (4 Marks)

- 2. Discuss different VLSI Design Styles in use for implementing digital logic on Integrated Circuits. (3 Marks)

- **(b)** What is the use of EDA tools? List the name of the companies in the business of developing EDA tools for VLSI. What is the role of following EDA tools in FPGA based logic design?

- **Behavioral Synthesis** a.

- b. **RTL Synthesis**

- Translate c.

- d. Mapping

- Place and Route (PAR) e.

- Q.3 Prepare the PLA programming table to realize following Boolean functions. 07 **(a)** Draw the structure of the programmed PLA to produce normal output. Calculate the total number of programmable links of the PLA.

$$F_1 = \sum(3,4,6,7)$$

$$F_2 = \prod(0,1,3,5,7)$$

$$F_3' = \sum(5,7)$$

Draw and explain the basic architecture of FPGA. What are the advance **(b)** 07 features available in current FPGA devices?

## OR

- Q.3 What is the basic building block of any CPLD? Draw and explain the 07 **(a)** construction of any standard CPLD device?

- Optimize the Boolean function F = A + B + ACD for minimum hardware 07 **(b)** and then implement F using 2x1 MUX as well as 2 i/p LUT. Write the behavioral VHDL code (architecture only) for implementing F.

- Define Event-Driven Simulator and Cycle-Based Simulators. Discuss the **Q.4** 07 **(a)** operation of event based simulator with suitable example.

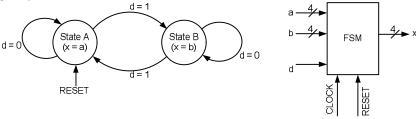

- **(b)** Write a VHDL description for the state machine given below using FSM 07 design style.

0.4

**(a)**

- 1. What is synthesis? How behavioral synthesis is different from RTL 07 synthesis? (3 Marks)

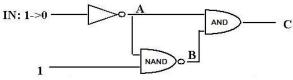

- 2. Explain the activity at node C in reference to delta-delay simulation in VHDL. How many deltas are needed to evaluate C? (4 Marks)

- Describe a decade counter in VHDL using FSM technique which will count **(b)** 07 up at every positive edge of the clock. If RESET is asserted, counter should start from zero.

- What is HDL? Discuss the relative differences between two widely used **Q.5** 07 **(a)** HDLs - VHDL and Verilog.

- Write VHDL description for negative edge triggered 4-bit shift register with 07 **(b)** active low asynchronous LOAD input, which should load the register with binary pattern õl 110ö. If DIR i/p is ÷1øthen perform shift left else shift right operation. DIR is synchronous i/p.

## (a) Explain following VHDL constructs ó

Q.5

- a. GUARDED BLOCK Statement

- b. GENERATE Statement

- (b) Discuss the issues to be taken care while modeling the simulation in VHDL. 07

\*\*\*\*\*